# MCP6S91/2/3

## Single-Ended, Rail-to-Rail I/O, Low-Gain PGA

#### **Features**

• Multiplexed Inputs: 1 or 2 channels

• 8 Gain Selections:

- +1, +2, +4, +5, +8, +10, +16 or +32 V/V

Serial Peripheral Interface (SPI<sup>™</sup>)

· Rail-to-Rail Input and Output

• Low Gain Error: ±1% (max.)

• Offset Mismatch Between Channels: 0 μV

• High Bandwidth: 1 to 18 MHz (typ.)

Low Noise: 10 nV/√Hz @ 10 kHz (typ.)

• Low Supply Current: 1.0 mA (typ.)

• Single Supply: 2.5V to 5.5V

Extended Temperature Range: -40°C to +125°C

## **Typical Applications**

• A/D Converter Driver

Multiplexed Analog Applications

Data Acquisition

• Industrial Instrumentation

Test Equipment

· Medical Instrumentation

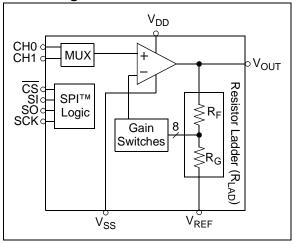

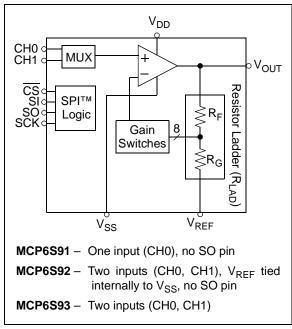

#### **Block Diagram**

### **Description**

The Microchip Technology Inc. MCP6S91/2/3 are analog Programmable Gain Amplifiers (PGAs). They can be configured for gains from +1 V/V to +32 V/V and the input multiplexer can select one of up to two channels through a SPI port. The serial interface can also put the PGA into shutdown to conserve power. These PGAs are optimized for high-speed, low offset voltage and single-supply operation with rail-to-rail input and output capability. These specifications support single-supply applications needing flexible performance or multiple inputs.

The one-channel MCP6S91 and the two-channel MCP6S92 are available in 8-pin PDIP, SOIC and MSOP packages. The two-channel MCP6S93 is available in a 10-pin MSOP package. All parts are fully specified from -40°C to +125°C.

## **Package Types**

| MCP6S9<br>PDIP, SOIC,                                         |                                            | MCP6S93<br>MSOP                                            |                                             |  |  |  |

|---------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------|---------------------------------------------|--|--|--|

| V <sub>OUT</sub> 1 CH0 2 V <sub>REF</sub> 3 V <sub>SS</sub> 4 | 8 V <sub>DD</sub><br>7 SCK<br>6 SI<br>5 CS | V <sub>OUT</sub> 1<br>CH0 2<br>CH1 3<br>V <sub>REF</sub> 4 | 10 V <sub>DD</sub><br>9 SCK<br>8 SO<br>7 SI |  |  |  |

| MCP6S9<br>PDIP, SOIC, I                                       |                                            | V <sub>SS</sub> 5                                          | 6 CS                                        |  |  |  |

| Vout 1 CH0 2 CH1 3 Vss 4                                      | 8 V <sub>DD</sub><br>7 SCK<br>6 SI<br>5 CS |                                                            |                                             |  |  |  |

## 1.0 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings †**

| V <sub>DD</sub> – V <sub>SS</sub>       | 7.0V                              |

|-----------------------------------------|-----------------------------------|

| == **                                   |                                   |

| All inputs and outputsV <sub>SS</sub> – | $0.3V \text{ to } V_{DD} + 0.3V$  |

| Difference Input voltage                | V <sub>DD</sub> - V <sub>SS</sub> |

| Output Short Circuit Current            | continuous                        |

| Current at Input Pin                    | ±2 mA                             |

| Current at Output and Supply Pins       | ±30 mA                            |

| Storage temperature                     | 65°C to +150°C                    |

| Junction temperature                    | +150°C                            |

| ESD protection on all pins (HBM; MM)    | ≥ 4 kV; 200V                      |

|                                         |                                   |

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## **PIN FUNCTION TABLE**

| Name                                  | Function               |  |  |  |

|---------------------------------------|------------------------|--|--|--|

| V <sub>OUT</sub>                      | Analog Output          |  |  |  |

| CH0, CH1                              | Analog Inputs          |  |  |  |

| $V_{REF}$                             | External Reference Pin |  |  |  |

| V <sub>SS</sub> Negative Power Supply |                        |  |  |  |

| CS                                    | SPI Chip Select        |  |  |  |

| SI                                    | SPI Serial Data Input  |  |  |  |

| SO                                    | SPI Serial Data Output |  |  |  |

| SCK SPI Clock Input                   |                        |  |  |  |

| $V_{DD}$                              | Positive Power Supply  |  |  |  |

## DC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to  $+5.5\underline{V}$ ,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_I = 10 \text{ k}\Omega$  to  $V_{DD}/2$ , SI and SCK are tied low and  $\overline{CS}$  is tied high.

| input = $CHO = (0.5V)/G$ , $CHI = 0.5V$ , $K_L = 10 \text{ kgz to } V_{DD}/Z$ , $SI$ and $SCK$ are the low and $CS$ is the dilight. |                |                              |                |                      |                |        |                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|----------------|----------------------|----------------|--------|------------------------------------------------------|

| Parameters                                                                                                                          |                | Sym                          | Min            | Тур                  | Max            | Units  | Conditions                                           |

| Amplifier Inputs (CH0, C                                                                                                            | H1)            |                              |                |                      |                |        |                                                      |

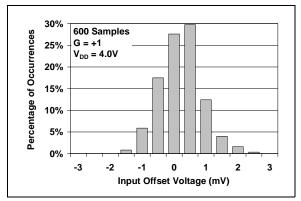

| Input Offset Voltage                                                                                                                |                | Vos                          | -4             | _                    | +4             | mV     | G = +1                                               |

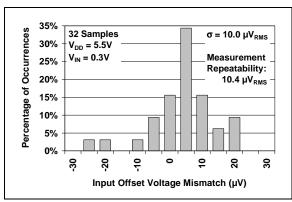

| Input Offset Voltage Mism                                                                                                           | atch           | ΔV <sub>OS</sub>             | _              | 0                    | _              | μV     | Between inputs (CH0, CH1)                            |

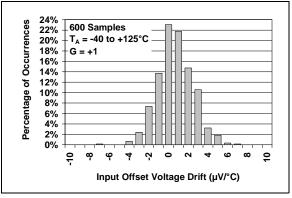

| Input Offset Voltage Drift                                                                                                          |                | $\Delta V_{OS}/\Delta T_{A}$ | _              | ±1.8                 | _              | μV/°C  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |

| Power Supply Rejection R                                                                                                            | Ratio          | PSRR                         | 70             | 90                   | _              | dB     | G = +1 (Note 1)                                      |

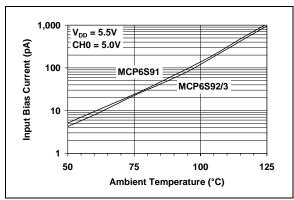

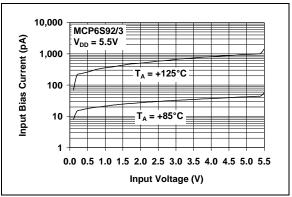

| Input Bias Current                                                                                                                  |                | Ι <sub>Β</sub>               |                | ±1                   |                | pА     | $CHx = V_{DD}/2$                                     |

| Input Bias Current at                                                                                                               |                | Ι <sub>Β</sub>               | _              | 30                   | _              | pА     | $CHx = V_{DD}/2, T_A = +85^{\circ}C$                 |

| Temperature                                                                                                                         |                | Ι <sub>Β</sub>               | _              | 600                  | _              | pА     | $CHx = V_{DD}/2, T_A = +125^{\circ}C$                |

| Input Impedance                                                                                                                     |                | Z <sub>IN</sub>              |                | 10 <sup>13</sup>   7 |                | Ω  pF  |                                                      |

| Input Voltage Range                                                                                                                 |                | $V_{IVR}$                    | $V_{SS} - 0.3$ | _                    | $V_{DD} + 0.3$ | V      | (Note 2)                                             |

| Reference Input (V <sub>REF</sub> )                                                                                                 |                |                              |                |                      |                |        |                                                      |

| Input Impedance                                                                                                                     |                | Z <sub>IN_REF</sub>          |                | (5/G)  6             |                | kΩ  pF |                                                      |

| Voltage Range                                                                                                                       |                | $V_{IVR\_REF}$               | $V_{SS}$       | 1                    | $V_{DD}$       | V      | (Note 2)                                             |

| Amplifier Gain                                                                                                                      |                |                              |                |                      |                |        |                                                      |

| Nominal Gains                                                                                                                       |                | G                            |                | 1 to 32              |                | V/V    | +1, +2, +4, +5, +8, +10, +16 or +32                  |

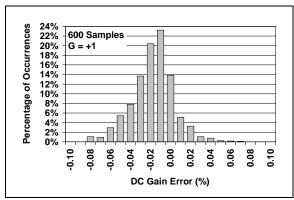

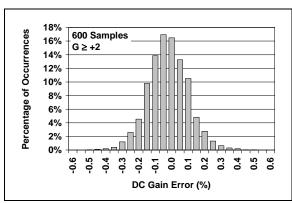

| DC Gain Error                                                                                                                       | G = +1         | 9 <sub>E</sub>               | -0.2           | _                    | +0.2           | %      | $V_{OUT} \approx 0.3V$ to $V_{DD} - 0.3V$            |

|                                                                                                                                     | G ≥ <b>+</b> 2 | 9 <sub>E</sub>               | -1.0           |                      | +1.0           | %      | $V_{OUT} \approx 0.3V$ to $V_{DD} - 0.3V$            |

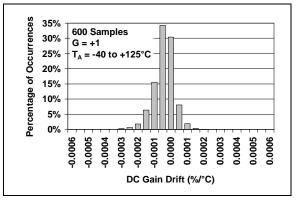

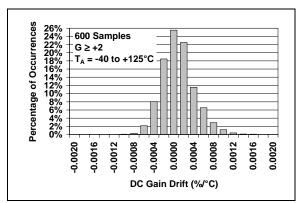

| DC Gain Drift                                                                                                                       | G = +1         | $\Delta G/\Delta T_A$        | _              | ±0.0002              | _              | %/°C   | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |

|                                                                                                                                     | G ≥ <b>+</b> 2 | $\Delta G/\Delta T_A$        | _              | ±0.0004              | _              | %/°C   | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

- Note 1: R<sub>LAD</sub> (R<sub>F</sub>+R<sub>G</sub> in Figure 4-1) connects V<sub>REF</sub>, V<sub>OUT</sub> and the inverting input of the internal amplifier. The MCP6S92 has V<sub>REF</sub> tied internally to V<sub>SS</sub>, so V<sub>SS</sub> is coupled to the internal amplifier and the PSRR spec describes PSRR+ only. It is recommended that the MCP6S92's V<sub>SS</sub> pin be tied directly to ground to avoid noise problems.

- 2: The MCP6S92's  $V_{IVR}$  and  $V_{IVR\_REF}$  are not tested in production; they are set by design and characterization.

- 3: I<sub>Q</sub> includes current in R<sub>LAD</sub> (typically 60 µA at V<sub>OUT</sub> = 0.3V). Both I<sub>Q</sub> and I<sub>Q</sub> SHDN exclude digital switching currents.

## DC CHARACTERISTICS (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10 \text{ k}\Omega$  to  $V_{DD}/2$ , SI and SCK are tied low and  $\overline{CS}$  is tied high.

| The first = 0.10 = (0.00 // 6, 0.11 = 0.00 /, NC = 10 1022 0 VDD/2, 0.14 nd 0.01 0 104 0 104 0 104 0 104 11911. |                             |                      |        |                       |          |                                                                                 |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|--------|-----------------------|----------|---------------------------------------------------------------------------------|

| Parameters                                                                                                      | Sym                         | Min                  | Тур    | Max                   | Units    | Conditions                                                                      |

| Ladder Resistance                                                                                               |                             |                      |        |                       |          |                                                                                 |

| Ladder Resistance                                                                                               | R <sub>LAD</sub>            | 3.4                  | 4.9    | 6.4                   | kΩ       | (Note 1)                                                                        |

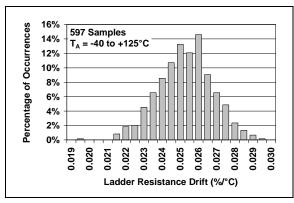

| Ladder Resistance across<br>Temperature                                                                         | $\Delta R_{LAD}/\Delta T_A$ | _                    | +0.028 | _                     | %/°C     | $T_A = -40$ °C to +125°C (Note 1)                                               |

| Amplifier Output                                                                                                |                             |                      |        |                       |          |                                                                                 |

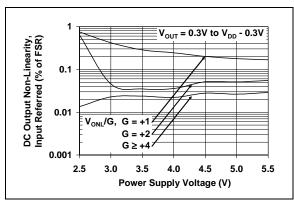

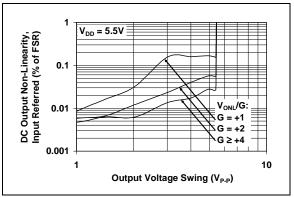

| DC Output Non-linearity G = +1                                                                                  | V <sub>ONL</sub>            | _                    | ±0.18  | _                     | % of FSR | $V_{OUT} \approx 0.3 \text{V to } V_{DD} - 0.3 \text{V}, V_{DD} = 5.0 \text{V}$ |

| G ≥ +2                                                                                                          | $V_{ONL}$                   | _                    | ±0.050 | _                     | % of FSR | $V_{OUT} \approx 0.3 \text{V to } V_{DD} - 0.3 \text{V}, V_{DD} = 5.0 \text{V}$ |

| Maximum Output Voltage Swing                                                                                    | V <sub>OH_ANA</sub> ,       | V <sub>SS</sub> + 20 |        | V <sub>DD</sub> – 100 | mV       | G ≥ +2; 0.5V output overdrive                                                   |

|                                                                                                                 | V <sub>OL_ANA</sub>         | V <sub>SS</sub> + 60 | _      | V <sub>DD</sub> – 60  |          | $G \ge +2$ ; 0.5V output overdrive,<br>$V_{REF} = V_{DD}/2$                     |

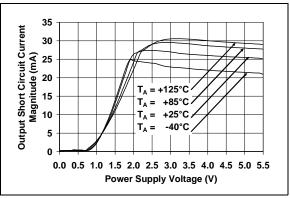

| Short Circuit Current                                                                                           | I <sub>SC</sub>             | _                    | ±25    | _                     | mA       |                                                                                 |

| Power Supply                                                                                                    |                             |                      |        |                       |          |                                                                                 |

| Supply Voltage                                                                                                  | $V_{DD}$                    | 2.5                  | _      | 5.5                   | V        |                                                                                 |

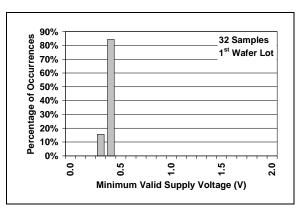

| Minimum Valid Supply Voltage                                                                                    | $V_{DD\_VAL}$               | _                    | 0.4    | 2.0                   | V        | Register data still valid                                                       |

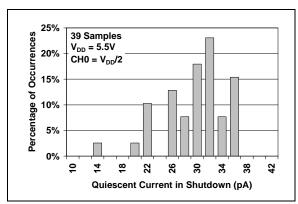

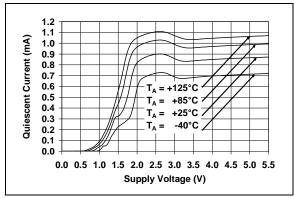

| Quiescent Current                                                                                               | ΙQ                          | 0.4                  | 1.0    | 1.6                   | mA       | I <sub>O</sub> = 0 (Note 3)                                                     |

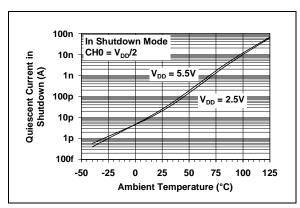

| Quiescent Current, Shutdown<br>Mode                                                                             | I <sub>Q_SHDN</sub>         |                      | 30     |                       | pA       | I <sub>O</sub> = 0 (Note 3)                                                     |

- Note 1: R<sub>LAD</sub> (R<sub>F</sub>+R<sub>G</sub> in Figure 4-1) connects V<sub>REF</sub>, V<sub>OUT</sub> and the inverting input of the internal amplifier. The MCP6S92 has V<sub>REF</sub> tied internally to V<sub>SS</sub>, so V<sub>SS</sub> is coupled to the internal amplifier and the PSRR spec describes PSRR+ only. It is recommended that the MCP6S92's V<sub>SS</sub> pin be tied directly to ground to avoid noise problems.

- 2: The MCP6S92's  $V_{IVR}$  and  $V_{IVR\_REF}$  are not tested in production; they are set by design and characterization.

- 3:  $I_Q$  includes current in  $R_{LAD}$  (typically 60  $\mu$ A at  $V_{OUT}$  = 0.3V). Both  $I_Q$  and  $I_{Q\_SHDN}$  exclude digital switching currents.

### AC CHARACTERISTICS

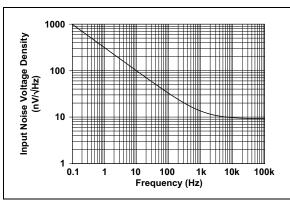

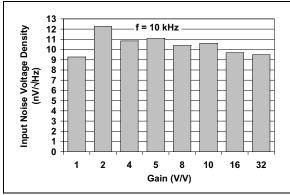

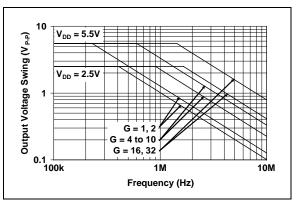

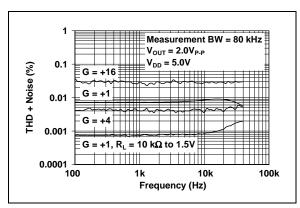

**Electrical Specifications:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L$  = 10 k $\Omega$  to  $V_{DD}/2$ ,  $C_L$  = 60 pF, SI and SCK are tied low and  $\overline{CS}$  is tied high. Max Sym Min Тур Units **Conditions Parameters** Frequency Response All gains; V<sub>OUT</sub> < 100 mV<sub>P-P</sub> (Note 1) -3 dB Bandwidth BW MHz 1 to 18 Gain Peaking **GPK** 0 dB All gains;  $V_{OUT} < 100 \text{ mV}_{P-P}$ **Total Harmonic Distortion plus Noise** f = 20 kHz. G = +1 V/V $V_{OUT} = 1.5V \pm 1.0 V_{PK}, V_{DD} = 5.0V,$ THD+N 0.0011 BW = 80 kHz,  $R_L = 10 \text{ k}\Omega$  to 1.5V  $V_{OUT} = 2.5V \pm 1.0 V_{PK}, V_{DD} = 5.0V, BW = 80 kHz$ f = 20 kHz, G = +1 V/VTHD+N 0.0089 f = 20 kHz, G = +4 V/VTHD+N  $V_{OUT} = 2.5V \pm 1.0 V_{PK}, V_{DD} = 5.0V,$ 0.0045 % BW = 80 kHzf = 20 kHz, G = +16 V/VTHD+N 0.028  $V_{OUT} = 2.5V \pm 1.0 V_{PK}, V_{DD} = 5.0V,$ BW = 80 kHzStep Response Slew Rate SR 4.0 V/µs G = 1, 211 G = 4, 5, 8, 10V/µs 22 V/µs G = 16, 32Noise f = 0.1 Hz to 10 Hz (Note 2)Input Noise Voltage  $E_{ni}$ 4.5 f = 0.1 Hz to 200 kHz (Note 2)30 Input Noise Voltage Density 10 nV/√Hz f = 10 kHz (Note 2)  $e_{ni}$ Input Noise Current Density 4  $fA/\sqrt{Hz}$  f = 10 kHzi<sub>ni</sub>

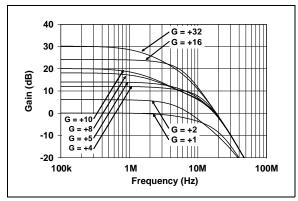

Note 1: See Table 4-1 for a list of typical numbers and Figure 2-25 for the frequency response versus gain.

<sup>2:</sup> E<sub>ni</sub> and e<sub>ni</sub> include ladder resistance noise. See Figure 2-12 for e<sub>ni</sub> versus G data.

### DIGITAL CHARACTERISTICS

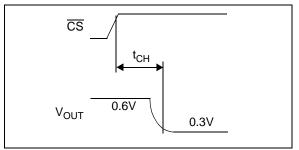

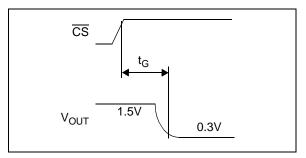

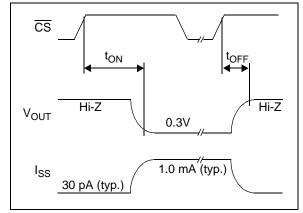

**Electrical Specifications:** Unless otherwise indicated,  $T_A = 25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GN\underline{D}$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10 \text{ k}\Omega$  to  $V_{DD}/2$ ,  $C_L = 60 \text{ pF}$ , SI and SCK are tied low and  $\overline{CS}$  is tied high. **Units Parameters** Sym Min Тур Max Conditions SPI Inputs (CS, SI, SCK) Logic Threshold, Low  $V_{IL}$  $0.3V_{DD}$ -1.0 Input Leakage Current  $I_{IL}$ +1.0 μΑ Logic Threshold, High ٧  $0.7 V_{DD}$  $V_{IH}$  $V_{DD}$ Amplifier Output Leakage Current -1.0 1.0 μΑ In Shutdown mode SPI Output (SO, for MCP6S93)  $V_{S\underline{S}}$ Logic Threshold, Low V<sub>SS</sub>+0.4 V  $V_{\text{OL\_DIG}}$  $I_{OL} = 2.1 \text{ mA}, V_{DD} = 5 \text{V}$ ٧  $V_{DD} - 0.5$ Logic Threshold, High V<sub>OH DIG</sub>  $V_{DD}$  $I_{OH} = -400 \, \mu A$ **SPI Timing** Pin Capacitance  $\mathsf{C}_{\mathsf{P}\underline{\mathsf{IN}}}$ 10 All digital I/O pins pF Input Rise/Fall Times (CS, SI, SCK) 2 (Note 1) μs  $t_{RFI}$ Output Rise/Fall Times (SO) 5 ns MCP6S93  $t_{RFO}$ CS High Time 40 ns t<sub>CSH</sub> SCK Edge to CS Fall Setup Time SCK edge when CS is high 10 t<sub>CS0</sub> ns CS Fall to First SCK Edge Setup Time 40 ns tcssc SCK Frequency 10 MHz V<sub>DD</sub> = 5V (Note 2)  $f_{SCK}$ SCK High Time 40  $t_{HI}$ ns SCK Low Time 40  $t_{\text{LO}}$ ns SCK Last Edge to CS Rise Setup Time 30 ns t<sub>SCCS</sub> CS Rise to SCK Edge Setup Time 100 SCK edge when CS is high t<sub>CS1</sub> ns SI Setup Time 40  $t_{SU}$ ns SI Hold Time 10 ns  $t_{HD}$ SCK to SO Valid Propagation Delay 80 ns **MCP6S93**  $t_{DO}$ CS Rise to SO Forced to Zero 80 MCP6S93 ns tsoz **Channel and Gain Select Timing** Channel Select Time CHx = 0.6V, CHy = 0.3V, G = 1, 15  $t_{CH}$ μs CHx to CHy select,  $\overline{\text{CS}} = 0.7 \text{ V}_{\text{DD}} \text{ to V}_{\text{OUT}} 90\% \text{ point}$ Gain Select Time 1 μs CHx = CHy = 0.3V $t_{\mathsf{G}}$ G = 5 to G = 1 select,  $\overline{\text{CS}} = 0.7 \text{ V}_{\text{DD}} \text{ to V}_{\text{OUT}} 90\% \text{ point}$ **Shutdown Mode Timing** Out of Shutdown mode (CS goes high)  $\overline{\text{CS}} = 0.7 \text{ V}_{\text{DD}} \text{ to V}_{\text{OUT}} 90\% \text{ point}$ 3.5 10 μs  $t_{ON}$ to Amplifier Output Turn-on Time Into Shutdown mode (CS goes high) to  $\overline{\text{CS}} = 0.7 \text{ V}_{\text{DD}} \text{ to V}_{\text{OUT}} 90\% \text{ point}$ 1.5 tOFF μs

Amplifier Output High-Z Turn-off Time

Note 1: Not tested in production. Set by design and characterization.

When using the device in the daisy-chain configuration, maximum clock frequency is determined by a combination of propagation delay time (t<sub>DO</sub> ≤ 80 ns), data input set-up time (t<sub>SU</sub> ≥ 40 ns), SCK high time (t<sub>HI</sub> ≥ 40 ns) and SCK rise and fall times of 5 ns. Maximum f<sub>SCK</sub> is therefore ≈ 5.8 MHz.

## **TEMPERATURE CHARACTERISTICS**

| <b>Electrical Specifications:</b> Unless otherwise indicated, $V_{DD} = +2.5V$ to $+5.5V$ , $V_{SS} = GND$ . |                |     |     |      |       |            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|----------------|-----|-----|------|-------|------------|--|--|--|--|

| Parameters                                                                                                   | Sym            | Min | Тур | Max  | Units | Conditions |  |  |  |  |

| Temperature Ranges                                                                                           |                |     |     |      |       |            |  |  |  |  |

| Specified Temperature Range                                                                                  | T <sub>A</sub> | -40 | _   | +125 | °C    | (Note 1)   |  |  |  |  |

| Operating Temperature Range                                                                                  | T <sub>A</sub> | -40 | _   | +125 | °C    |            |  |  |  |  |

| Storage Temperature Range                                                                                    | T <sub>A</sub> | -65 | _   | +150 | °C    |            |  |  |  |  |

| Thermal Package Resistances                                                                                  |                |     |     |      |       |            |  |  |  |  |

| Thermal Resistance, 8L-PDIP                                                                                  | $\theta_{JA}$  | _   | 85  | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 8L-SOIC                                                                                  | $\theta_{JA}$  | _   | 163 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 8L-MSOP                                                                                  | $\theta_{JA}$  | _   | 206 | _    | °C/W  |            |  |  |  |  |

| Thermal Resistance, 10L-MSOP                                                                                 | $\theta_{JA}$  | _   | 143 | _    | °C/W  |            |  |  |  |  |

**Note 1:** Operation in this range must not cause T<sub>J</sub> to exceed Maximum Junction Temperature (+150°C).

FIGURE 1-1: Channel Select Timing Diagram.

FIGURE 1-3: Gain Select Timing Diagram.

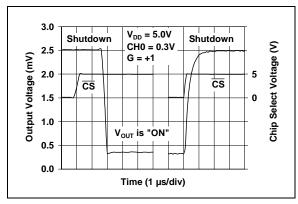

FIGURE 1-2: PGA Shutdown Timing

Diagram (must enter correct commands before

CS goes high).

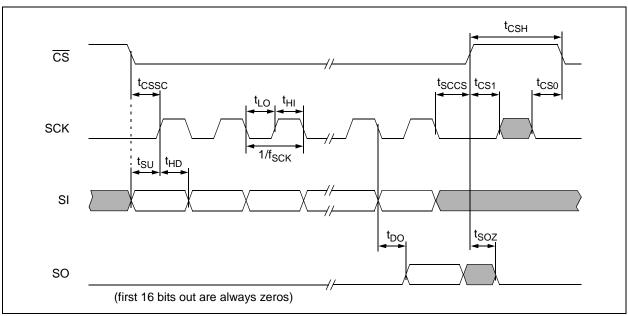

FIGURE 1-4: Detailed SPI™ Serial Interface Timing; SPI 0,0 Mode.

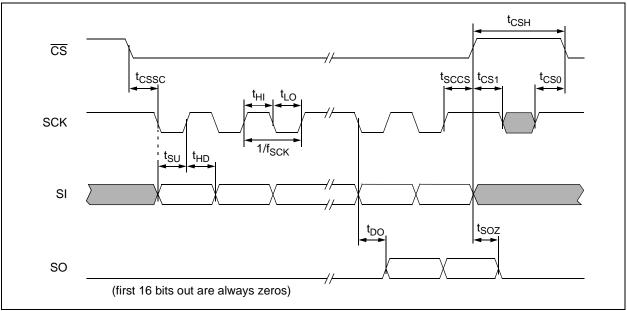

FIGURE 1-5: Detailed SPI™ Serial Interface Timing; SPI 1,1 Mode.

## 1.1 DC Output Voltage Specs / Model

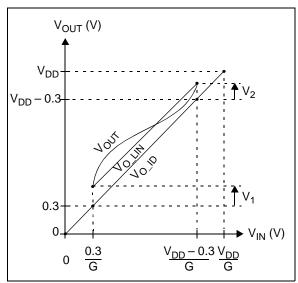

## 1.1.1 IDEAL MODEL

The ideal PGA output voltage (V<sub>OUT</sub>) is:

#### **EQUATION 1-1:**

$$V_{O\_ID} = G_{VIN}$$

$V_{REF} = V_{SS} = 0V$

Where:

G is the nominal gain

(see Figure 1-6). This equation holds when there are no gain or offset errors and when the  $V_{REF}$  pin is tied to a low-impedance source (<< 0.1 $\Omega$ ) at ground potential ( $V_{SS}$  = 0V).

#### 1.1.2 LINEAR MODEL

The PGA's linear region of operation, including offset and gain errors, is modeled by the line  $V_{O\_LIN}$  shown in Figure 1-6.

#### **EQUATION 1-2:**

$$\begin{split} V_{O\_LIN} &= G(I+g_E) \bigg( V_{IN} - \frac{0.3 \, V}{G} + V_{OS} \bigg) + 0.3 \, V \\ V_{REF} &= V_{SS} = O V \end{split}$$

The end points of this line are at  $V_{O\_ID} = 0.3V$  and  $V_{DD} - 0.3V$ . Figure 1-6 shows the relationship between the gain and offset specifications referred to in the electrical specifications as follows:

#### **EQUATION 1-3:**

$$g_E = 100\% \frac{V_2 - V_1}{G(V_{DD} - 0.6V)}$$

$V_{OS} = \frac{V_1}{G(1 + g_E)}$   $G = +1$

The DC Gain Drift  $(\Delta G/\Delta T_A)$  can be calculated from the change in  $g_E$  across temperature. This is shown in the following equation:

### **EQUATION 1-4:**

$$\Delta G/\Delta T_A = \frac{\Delta g_E}{\Delta T_A}$$

**FIGURE 1-6:** Output Voltage Model with the standard condition  $V_{REF} = V_{SS} = 0V$ .

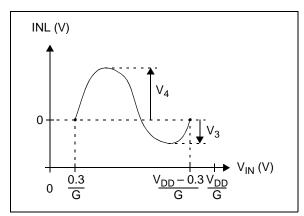

#### 1.1.3 OUTPUT NON-LINEARITY

Figure 1-7 shows the Integral Non-Linearity (INL) of the output voltage.

#### **EQUATION 1-5:**

$$INL = V_{OUT} - V_{O\ LIN}$$

The output non-linearity specification in the Electrical Specifications (with units of: % of FSR) is related to Figure 1-7 by:

#### **EQUATION 1-6:**

$$V_{ONL} = \frac{max(V_3, V_4)}{V_{DD} - 0.6V} \cdot 100\%$$

The Full-Scale Range (FSR) is  $V_{DD} - 0.6V$  (0.3V to  $V_{DD} - 0.3V$ ).

**FIGURE 1-7:** Output Voltage INL with the standard condition  $V_{REF} = V_{SS} = 0$  V.

## 1.1.4 DIFFERENT V<sub>REF</sub> CONDITIONS

Some of the plots in Section 2.0 "Typical Performance Curves", have the conditions  $V_{REF} = V_{DD}/2$  or  $V_{REF} = V_{DD}$ . The equations and figures above are easily modified for these conditions. The ideal  $V_{OUT}$  equation becomes:

### **EQUATION 1-7:**

$$\begin{split} V_{O\_ID} &= V_{REF} + G(V_{IN} - V_{REF}) \\ V_{DD} &\geq V_{REF} > V_{SS} = 0 V \end{split}$$

The complete linear model is:

### **EQUATION 1-8:**

$$V_{ON\_LIN} = G(1 + g_E)(V_{IN} - V_{IN\_L} + V_{OS}) + 0.3V$$

$$V_{REF} = V_{SS} = 0V$$

where the new V<sub>IN</sub> end points are:

#### **EQUATION 1-9:**

$$\begin{split} V_{IN\_L} &= \frac{0.3V - V_{REF}}{G} + V_{REF} \\ V_{IN\_H} &= \frac{V_{DD} - 0.3V - V_{REF}}{G} + V_{REF} \end{split}$$

The equations for extracting the specifications do not change.

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10 \text{ k}\Omega$  to  $V_{DD}/2$  and  $C_L = 60 \text{ pF}$ .

**FIGURE 2-1:** DC Gain Error, G = +1.

**FIGURE 2-2:** DC Gain Error,  $G \ge +2$ .

FIGURE 2-3: Ladder Resistance Drift.

**FIGURE 2-4:** DC Gain Drift, G = +1.

**FIGURE 2-5:** DC Gain Drift,  $G \ge +2$ .

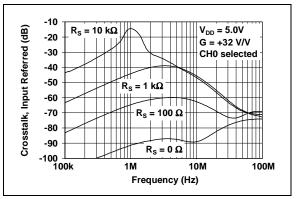

FIGURE 2-6: Crosstalk vs. Frequency (circuit in Figure 6-4).

**Note:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10 \text{ k}\Omega$  to  $V_{DD}/2$  and  $C_L = 60 \text{ pF}$ .

**FIGURE 2-7:** Input Offset Voltage,  $V_{DD} = 4.0V$ .

FIGURE 2-8: Input Offset Voltage Mismatch.

FIGURE 2-9: Input Noise Voltage Density vs. Frequency.

FIGURE 2-10: Input Offset Voltage Drift.

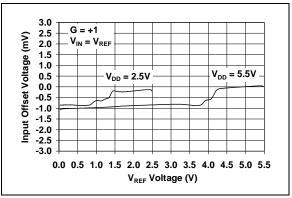

**FIGURE 2-11:** Input Offset Voltage vs.  $V_{REF}$  Voltage.

FIGURE 2-12: Input Noise Voltage Density vs. Gain.

**Note:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10$  k $\Omega$  to  $V_{DD}/2$  and  $C_L = 60$  pF.

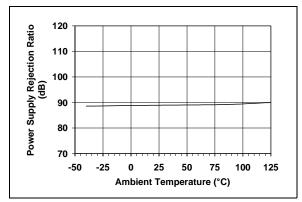

**FIGURE 2-13:** PSRR vs. Ambient Temperature.

**FIGURE 2-14:** Input Bias Current vs. Ambient Temperature.

**FIGURE 2-15:** Quiescent Current in Shutdown Mode vs. Ambient Temperature.

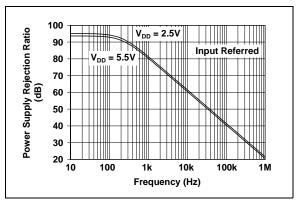

FIGURE 2-16: PSRR vs. Frequency.

FIGURE 2-17: Input Bias Current vs. Input Voltage.

**FIGURE 2-18:** Quiescent Current in Shutdown Mode.

**Note:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10$  k $\Omega$  to  $V_{DD}/2$  and  $C_L = 60$  pF.

**FIGURE 2-19:** Quiescent Current vs. Supply Voltage.

**FIGURE 2-20:** DC Output Non-Linearity vs. Supply Voltage.

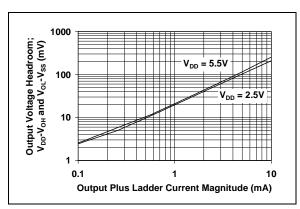

**FIGURE 2-21:** Output Voltage Headroom vs. Output Plus Ladder Current (circuit in Figure 4-2).

**FIGURE 2-22:** Output Short Circuit Current vs. Supply Voltage.

**FIGURE 2-23:** DC Output Non-Linearity vs. Output Swing.

**FIGURE 2-24:** Output Voltage Swing vs. Frequency.

$\label{eq:Note: Note: Unless otherwise indicated, T_A = +25°C, V_{DD} = +2.5V to +5.5V, V_{SS} = GND, V_{REF} = V_{SS}, G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V, R_L = 10 k\Omega to V_{DD}/2 and C_L = 60 pF.$

FIGURE 2-25: Gain vs. Frequency.

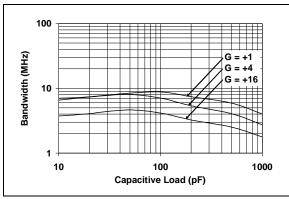

**FIGURE 2-26:** Bandwidth vs. Capacitive Load.

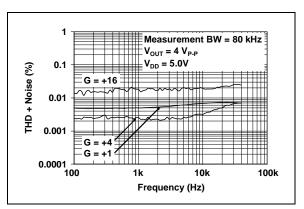

**FIGURE 2-27:** THD plus Noise vs. Frequency,  $V_{OUT} = 2 V_{P-P}$

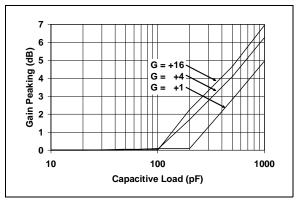

FIGURE 2-28: Gain Peaking vs. Capacitive Load.

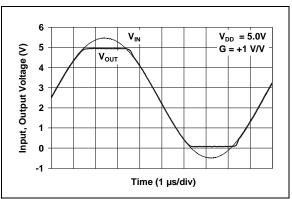

FIGURE 2-29: The MCP6S91/2/3 family shows no phase reversal under overdrive.

**FIGURE 2-30:** THD plus Noise vs. Frequency,  $V_{OUT} = 4 V_{P-P}$

**Note:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +2.5V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{REF} = V_{SS}$ , G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V,  $R_L = 10$  k $\Omega$  to  $V_{DD}/2$  and  $C_L = 60$  pF.

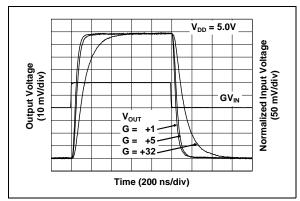

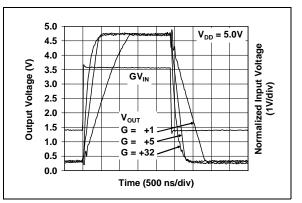

**FIGURE 2-31:** Small-Signal Pulse Response.

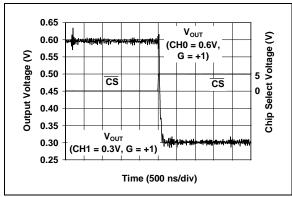

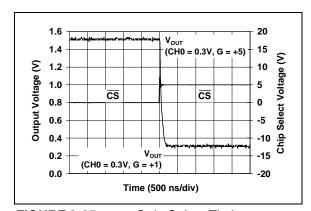

FIGURE 2-32: Channel Select Timing.

**FIGURE 2-33:** Output Voltage vs. Shutdown Mode.

**FIGURE 2-34:** Large-Signal Pulse Response.

FIGURE 2-35: Gain Select Timing.

**FIGURE 2-36:** Minimum Valid Supply Voltage (register data still valid).

$\label{eq:Note: Note: Unless otherwise indicated, T_A = +25°C, V_{DD} = +2.5V to +5.5V, V_{SS} = GND, V_{REF} = V_{SS}, G = +1 V/V, Input = CH0 = (0.3V)/G, CH1 = 0.3V, R_L = 10 k\Omega to V_{DD}/2 and C_L = 60 pF.$

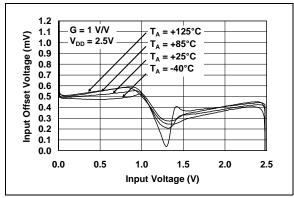

**FIGURE 2-37:** Input Offset Voltage vs. Input Voltage,  $V_{DD} = 2.5V$ .

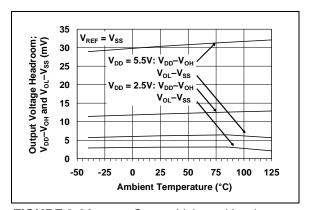

**FIGURE 2-38:** Output Voltage Headroom vs. Ambient Temperature.

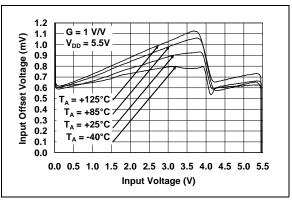

**FIGURE 2-39:** Input Offset Voltage vs. Input Voltage,  $V_{DD} = 5.5V$ .

## 3.0 PIN DESCRIPTIONS

Descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP6S91 | MCP6S92 | MCP6S93 | Symbol           | Description            |

|---------|---------|---------|------------------|------------------------|

| 1       | 1       | 1       | V <sub>OUT</sub> | Analog Output          |

| 2       | 2       | 2       | CH0              | Analog Input           |

| _       | 3       | 3       | CH1              | Analog Input           |

| 3       | _       | 4       | $V_{REF}$        | External Reference Pin |

| 4       | 4       | 5       | V <sub>SS</sub>  | Negative Power Supply  |

| 5       | 5       | 6       | CS               | SPI™ Chip Select       |

| 6       | 6       | 7       | SI               | SPI Serial Data Input  |

| _       | _       | 8       | SO               | SPI Serial Data Output |

| 7       | 7       | 9       | SCK              | SPI Clock Input        |

| 8       | 8       | 10      | $V_{DD}$         | Positive Power Supply  |

### 3.1 Analog Output

The output pin  $(V_{OUT})$  is a low-impedance voltage source. The selected gain (G), selected input (CH0, CH1) and voltage at  $V_{REF}$  determine its value.

## 3.2 Analog Inputs (CH0, CH1)

The inputs CH0 and CH1 connect to the signal sources. They are high-impedance CMOS inputs with low bias currents. The internal MUX selects which one is amplified to the output.

## 3.3 External Reference Voltage (V<sub>REF</sub>)

The  $V_{REF}$  pin, which is an analog input, should be at a voltage between  $V_{SS}$  and  $V_{DD}$  (the MCP6S92 has  $V_{REF}$  tied internally to  $V_{SS}$ ). The voltage at this pin shifts the output voltage.

## 3.4 Power Supply ( $V_{SS}$ and $V_{DD}$ )

The Positive Power Supply Pin ( $V_{DD}$ ) is 2.5V to 5.5V higher than the Negative Power Supply Pin ( $V_{SS}$ ). For normal operation, the other pins are at voltages between  $V_{SS}$  and  $V_{DD}$ .

Typically, these parts are used in a single (positive) supply configuration. In this case,  $V_{SS}$  is connected to ground and  $V_{DD}$  is connected to the supply.  $V_{DD}$  will need a local bypass capacitor (typically 0.01  $\mu F$  to 0.1  $\mu F)$  within 2 mm of the  $V_{DD}$  pin. These parts can share a bulk capacitor with analog parts (typically 2.2  $\mu F$  to 10  $\mu F)$  within 100 mm of the  $V_{DD}$  pin.

### 3.5 Digital Inputs

The SPI interface inputs are: Chip Select  $(\overline{CS})$ , Serial Input (SI) and Serial Clock (SCK). These are Schmitt-triggered, CMOS logic inputs.

## 3.6 Digital Output

The MCP6S93 device has a SPI interface Serial Output (SO) pin. This is a CMOS push-pull output and does not ever go High-Z. Once the device is deselected (CS goes high), SO is forced low. This feature supports daisy-chaining, as explained in **Section 5.3 "Daisy-Chain Configuration"**.

## 4.0 ANALOG FUNCTIONS

The MCP6S91/2/3 family of Programmable Gain Amplifiers (PGA) is based on simple analog building blocks (see Figure 4-1). Each of these blocks will be explained in more detail in the following subsections.

FIGURE 4-1: PGA Block Diagram.

### 4.1 Input MUX

The MCP6S91 has one input, while the MCP6S92 and MCP6S93 have two inputs (see Figure 4-1).

For the lowest input current, float unused inputs. Tying these pins to a voltage near the active channel's bias voltage also works well. For simplicity, they can be tied to  $V_{SS}$  or  $V_{DD}$ , but the input current may increase.

The one-channel MCP6S91 has approximately the same input bias current as the two-channel MCP6S92 and MCP6S93.

The input offset voltage mismatch between channels  $(\Delta V_{OS})$  is, ideally, 0  $\mu V$ . The input MUX uses CMOS transmission gates that have drain-source (channel) resistance, but no offset voltage. The histogram in Figure 2-8 reflects the measurement repeatability (i.e., noise power bandwidth) rather than the actual mismatch. Reducing the measurement bandwidth will produce a more narrow histogram and give an average closer to 0  $\mu V$ .

### 4.2 Internal Op Amp

The internal op amp gives the right combination of bandwidth, accuracy and flexibility.

#### 4.2.1 COMPENSATION CAPACITORS

The internal op amp has three compensation capacitors (comp. caps.) connected to a switching network. They are selected to give good small-signal bandwidth at high gains and good slew rates (full-power bandwidth) at low gains. The change in bandwidth as gain changes is between 2 and 12 MHz. Refer to Table 4-1 for more information.

TABLE 4-1: GAIN VS. INTERNAL COMPENSATION CAPACITOR

| Gain<br>(V/V) | Internal<br>Comp.<br>Cap. | GBWP<br>(MHz)<br>Typ. | SR<br>(V/µs)<br>Typ. | FPBW<br>(MHz)<br>Typ. | BW<br>(MHz)<br>Typ. |

|---------------|---------------------------|-----------------------|----------------------|-----------------------|---------------------|

| 1             | Large                     | 12                    | 4.0                  | 0.30                  | 12                  |

| 2             | Large                     | 12                    | 4.0                  | 0.30                  | 6                   |

| 4             | Medium                    | 20                    | 11                   | 0.70                  | 10                  |

| 5             | Medium                    | 20                    | 11                   | 0.70                  | 7                   |

| 8             | Medium                    | 20                    | 11                   | 0.70                  | 2.4                 |

| 10            | Medium                    | 20                    | 11                   | 0.70                  | 2.0                 |

| 16            | Small                     | 64                    | 22                   | 1.6                   | 5                   |

| 32            | Small                     | 64                    | 22                   | 1.6                   | 2.0                 |

- Note 1: FPBW is the Full-Power Bandwidth. These numbers are based on  $V_{DD} = 5.0V$ .

- 2: No changes in DC performance (e.g., V<sub>OS</sub>) accompany a change in compensation capacitor.

- BW is the closed-loop, small signal -3 dB bandwidth.

#### 4.2.2 RAIL-TO-RAIL CHANNEL INPUTS

The input stage of the internal op amp uses two differential input stages in parallel; one operates at low  $V_{IN}$  (input voltage), while the other operates at high  $V_{IN}.$  With this topology, the internal inputs can operate to 0.3V past either supply rail. The input offset voltage is measured at both  $V_{IN} = V_{SS} - 0.3 \text{V}$  and  $V_{DD} + 0.3 \text{V}$  to ensure proper operation.

The transition between the two input stages occurs when  $V_{IN} \approx V_{DD} - 1.5V$ . For the best distortion and gain linearity, avoid this region of operation.

#### 4.2.3 RAIL-TO-RAIL OUTPUT

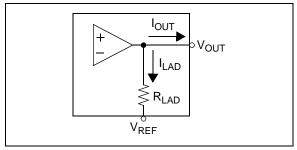

The maximum output voltage swing is the maximum swing possible under a particular amplifier load current. The amplifier load current is the sum of the external load current (I<sub>OUT</sub>) and the current through the ladder resistance (I<sub>LAD</sub>); see Figure 4-2.

#### **EQUATION 4-1:**

$$Amplifier Load Current = I_{OUT} + I_{LAD}$$

Where:

$$I_{LAD} = \frac{(V_{OUT} - V_{REF})}{R_{LAD}}$$

FIGURE 4-2: Amplifier Load Current.

See Figure 2-21 for the typical output headroom  $(V_{DD}-V_{OH} \text{ or } V_{OL}-V_{SS})$  as a function of amplifier load current.

The specification table states the output can reach within 60 mV of either supply rail when R<sub>L</sub> = 10 k $\Omega$  and V<sub>REF</sub> = V<sub>DD</sub>/2.

## 4.2.4 INPUT VOLTAGE AND PHASE REVERSAL

The MCP6S91/2/3 amplifier family is designed with CMOS input devices. It is designed to not exhibit phase inversion when the input pins exceed the supply voltages. Figure 2-29 shows an input voltage exceeding both supplies with no resulting phase inversion.

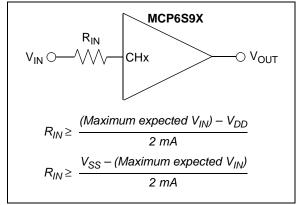

The maximum voltage that can be applied to the input pins (CHx) is  $V_{SS} - 0.3V$  to  $V_{DD} + 0.3V$ . Voltages on the inputs that exceed this absolute maximum rating can cause excessive current to flow into or out of the input pins. Current beyond  $\pm 2$  mA can cause possible reliability problems. Applications that exceed this rating must be externally limited with an input resistor, as shown in Figure 4-3.

**FIGURE 4-3:**  $R_{IN}$  limits the current flow into an input pin.

#### 4.3 Resistor Ladder

The resistor ladder shown in Figure 4-1  $(R_{LAD} = R_F + R_G)$  sets the gain. Placing the gain switches in series with the inverting input reduces the parasitic capacitance, distortion and gain mismatch.

$R_{LAD}$  is an additional load on the output of the PGA and causes additional current draw from the supplies. It is also a load  $(Z_{IN\_REF})$  on the external circuitry driving the  $V_{REF}$  pin.

In Shutdown mode,  $R_{LAD}$  is still attached to the  $V_{OUT}$  and  $V_{REF}$  pins. Thus, these pins and the internal amplifier's inverting input are all connected through  $R_{LAD}$  and the output is not High-Z (unlike the internal op amp).

While R<sub>LAD</sub> contributes to the output noise, its effect is small. Refer to Figure 2-12.

## 4.4 Rail-to-Rail V<sub>REF</sub> Input

The  $V_{REF}$  input is intended to be driven by a low-impedance voltage source. The source driving the  $V_{REF}$  pin should have an output impedance less than  $0.1\Omega$  to maintain reasonable gain accuracy. The supply voltage  $V_{SS}$  and  $V_{DD}$  usually meet this requirement.

$R_{LAD}$  presents a load at the  $V_{REF}$  pin to the external circuit ( $Z_{IN\_REF} \approx (5 \text{ k}\Omega/G)||(6 \text{ pF})$ ), which depends on the gain. Any source driving the  $V_{REF}$  pin must be capable of driving a load as heavy as 0.16 k $\Omega$ ||6 pF (G = 32).

The absolute maximum voltages that can be applied to the reference input pin ( $V_{REF}$ ) are  $V_{SS}-0.3V$  and  $V_{DD}+0.3V$ . Voltages on the inputs that exceed this absolute maximum rating can cause excessive current to flow into or out of this pin. Current beyond  $\pm 2$  mA can cause possible reliability problems. Because an external series resistor cannot be used (for low gain error), the external circuit *must* ensure that  $V_{REF}$  is between  $V_{SS}-0.3V$  and  $V_{DD}+0.3V$ .

The  $V_{IVR\_REF}$  spec shows the region of normal operation for the  $V_{REF}$  pin ( $V_{SS}$  to  $V_{DD}$ ). Staying within this region ensures proper operation of the PGA and its surrounding circuitry.

### 4.5 Shutdown Mode

These PGAs use a software shutdown command. When the SPI interface sends a shutdown command, the internal op amp is shut down and its output placed in a High-Z state.

The resistive ladder is always connected between  $V_{REF}$  and  $V_{OUT}$ ; even in shutdown. This means that the output resistance will be on the order of 5 k $\Omega$ , with a path for output signals to appear at the input.

#### 5.0 DIGITAL FUNCTIONS

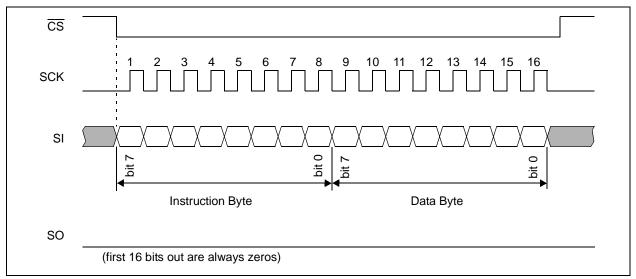

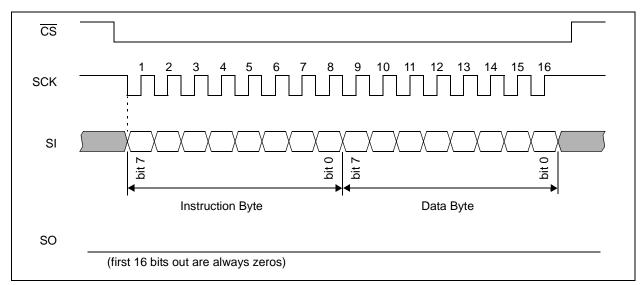

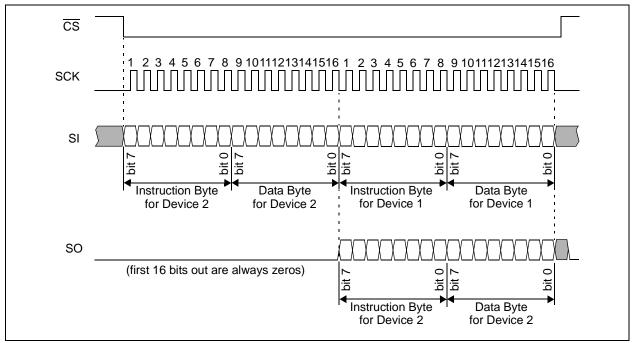

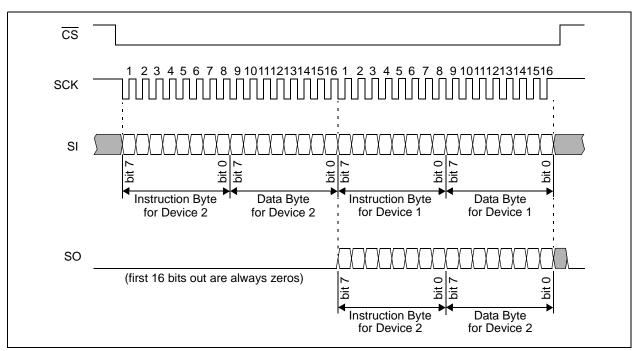

The MCP6S91/2/3 PGAs use a standard SPI compatible serial interface to receive instructions from a controller. This interface is configured to allow daisy-chaining with other SPI devices.

## 5.1 SPI Timing

Chip Select  $\overline{(CS)}$  toggles low to initiate communication with these devices. The first byte of each SI word (two bytes long) is the instruction byte, which goes into the Instruction register. The Instruction register points the second byte to its destination. In a typical application,  $\overline{CS}$  is raised after one word (16 bits) to implement the desired changes. Section 5.3 "Daisy-

**Chain Configuration**", covers applications using multiple 16-bit words. SO goes low after  $\overline{\text{CS}}$  goes high; it has a push-pull output that does not go into a high-Z state.

The MCP6S91/2/3 devices operate in SPI modes 0,0 and 1,1. In 0,0 mode, the clock idles in the low state (Figure 5-1). In 1,1 mode, the clock idles in the high state (Figure 5-2). In both modes, SI data is loaded into the PGA on the rising edge of SCK, while SO data is clocked out on the falling edge of SCK. In 0,0 mode, the falling edge of CS also acts as the first falling edge of SCK (see Figure 5-1). There must be multiples of 16 clocks (SCK) while CS is low or commands will abort (see Section 5.3 "Daisy-Chain Configuration").

FIGURE 5-1: Serial Bus Sequence for the PGA; SPI™ 0,0 Mode (see Figure 1-4).

FIGURE 5-2: Serial Bus Sequence for the PGA; SPI<sup>TM</sup> 1,1 Mode (see Figure 1-5).

## 5.2 Registers

The analog functions are programmed through the SPI interface using 16-bit words (see Figure 5-1 and Figure 5-2). This data is sent to two of three 8-bit registers: Instruction register (Register 5-1), Gain register (Register 5-2) and Channel register (Register 5-3). There are no power-up defaults for these three registers.

## 5.2.1 ENSURING VALID DATA IN THE REGISTERS

After power up, the registers contain random data that must be initialized. Sending valid gain and channel selection commands to the internal registers puts valid data into those registers. Also, the internal state machine starts in an arbitrary state. Toggling the Chip Select pin  $\overline{(CS)}$  from high to low, then back to high again, puts the internal state machine in a known, valid condition (this can be done by entering any valid command).

After power-up, and when the power supply voltage dips below the minimum valid  $V_{DD}$  ( $V_{DD\_VAL}$ ), the internal register data and state machine may need to be reset. This is accomplished as described before. Use an external system supervisor to detect these events so that the microcontroller will reset the PGA state and registers.

A 0.1  $\mu F$  bypass capacitor mounted as close as possible to the  $V_{DD}$  pin provides additional transient immunity.

#### 5.2.2 INSTRUCTION REGISTER

The Instruction register has 3 command bits and 1 indirect address bit; see Register 5-1. The command bits include a NOP (000) to support daisy-chaining (see Section 5.3 "Daisy-Chain Configuration"); the other NOP commands shown should not be used (they are reserved for future use). The device is brought out of Shutdown mode when a valid command, other than NOP or Shutdown, is sent and  $\overline{\text{CS}}$  is raised.

#### REGISTER 5-1: INSTRUCTION REGISTER

| W-0   | W-0 | W-0 | U-x | U-x | U-x | U-x | W-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| M2    | M1  | MO  | _   | _   | _   | _   | A0    |

| bit 7 |     |     |     |     |     |     | bit 0 |

#### bit 7-5 M2-M0: Command bits

000 = NOP (Note 1)

001 = PGA enters Shutdown mode as soon as a full 16-bit word is sent and  $\overline{CS}$  is raised.

(Notes 1 and 2)

010 = Write to register.

011 = NOP (reserved for future use) (Note 1)

1XX = NOP (reserved for future use) (Note 1)

## bit 4-1 **Unimplemented:** Read as '0' (reserved for future use)

bit 0 A0: Indirect Address bit

1 = Addresses the Channel register

0 = Addresses the Gain register

Note 1: All other bits in the 16-bit word (including A0) are "don't cares."

2: The device exits Shutdown mode when a valid command (other than NOP or Shutdown) is sent and  $\overline{CS}$  is raised; that valid command will be executed. Shutdown does not toggle.

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 5.2.3 SETTING THE GAIN

The amplifier can be programmed to produce binary and decimal gain settings between +1 V/V and +32 V/V. Register 5-2 shows the details. At the same time, different compensation capacitors are selected to optimize the bandwidth vs. slew rate trade-off (see Table 4-1).

### **REGISTER 5-2: GAIN REGISTER**

| U-x   | U-x | U-x | U-x | U-x | W-0 | W-0 | W-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | G2  | G1  | G0    |

| bit 7 |     |     |     |     |     |     | bit 0 |

## bit 7-3 Unimplemented: Read as '0' (reserved for future use)

bit 2-0 **G2-G0:** Gain Select bits

000 = Gain of +1

001 = Gain of +2

010 = Gain of +4

011 = Gain of +5

100 = Gain of +8

101 = Gain of +10

110 = Gain of +16

111 = Gain of +32

## Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 5.2.4 CHANGING THE CHANNEL

If the Instruction register is programmed to address the Channel register, the multiplexed inputs of the MCP6S92 and MCP6S93 can be changed using Register 5-3.

## REGISTER 5-3: CHANNEL REGISTER

| U-x   | U-x | U-x | U-x | U-x | U-x | U-x | W-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | C0    |

| bit 7 |     |     |     |     |     |     | bit 0 |

bit 7-1 **Unimplemented:** Read as '0' (reserved for future use)

bit 0 C0: Channel Select bit

|     | MCP6S91 | MCP6S92 | MCP6S93 |

|-----|---------|---------|---------|

| 0 = | CH0     | CH0     | CH0     |

| 1 = | CH0     | CH1     | CH1     |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 5.2.5 SHUTDOWN COMMAND

The software shutdown command allows the user to put the amplifier into a low-power mode (see Register 5-1). In this Shutdown mode, most pins are high-impedance (Section 4.5 "Shutdown Mode" and Section 5.1 "SPI Timing" cover the exceptions at pins  $V_{REF}$ ,  $V_{OUT}$  and SO).

Once the PGA has entered Shutdown mode, it will remain in this mode until either a valid command is sent to the device (other than NOP or Shutdown) or the device is powered down and back up again. The internal registers maintain their values while in shutdown.

Once brought out of Shutdown mode, the part returns to its previous state (see **Section 5.2.1 "Ensuring Valid Data in the Registers"** for exceptions to this rule). This makes it possible to bring the device out of shutdown mode using one command; send a command to select the current channel (or gain) and the device will exit shutdown with the same state that existed before shutdown.

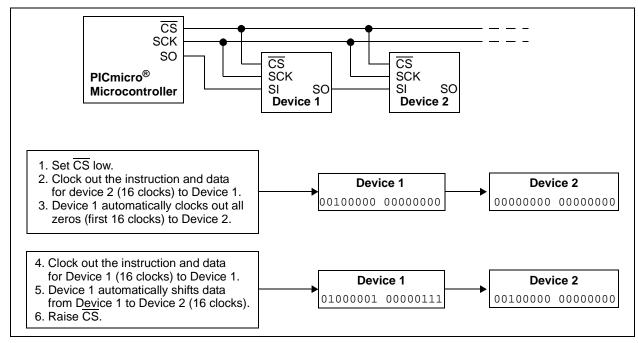

## 5.3 Daisy-Chain Configuration

Multiple MCP6S91/2/3 devices can be connected in a daisy-chain configuration by connecting the SO pin from one device to the SI  $\underline{\text{pin}}$  on the next device and using common SCK and  $\overline{\text{CS}}$  lines (Figure 5-3). This approach reduces PCB layout complexity and uses fewer PICmicro $^{\textcircled{\$}}$  microcontroller I/O pins.

The example in Figure 5-3 shows a daisy-chain configuration with two devices, although any number of devices can be configured this way. The MCP6S91 and MCP6S92 can only be used at the far end of the daisy-chain, because they do not have a serial data out (SO) pin. As shown in Figure 5-4 and Figure 5-5, both SI and SO data are sent in 16-bit (2 byte) words. These devices abort any command that is not a multiple of 16 bits.

When using the daisy-chain configuration, the maximum clock speed possible is reduced to  $\approx 5.8$  MHz due to the SO pin's propagation delay (see Electrical Specifications).

The internal SPI shift register is automatically loaded with zeros whenever  $\overline{\text{CS}}$  goes high (a command is executed). Thus, the first 16-bits out of the SO pin after the  $\overline{\text{CS}}$  line goes low are always zeros. This means that the first command loaded into the next device in the daisy-chain is a NOP. This feature makes it possible to send shorter command and data byte strings when the farthest devices do not need to change. For example, if there were three devices on the chain, and only the middle device needed changing, then only 32 bytes of data need to be transmitted (for the first and middle devices). The last device on the chain would receive a NOP when the  $\overline{\text{CS}}$  pin is raised to execute the command.

FIGURE 5-3: Daisy-Chain Configuration.

FIGURE 5-4: Serial Bus Sequence for Daisy-Chain Configuration; SPI™ 0,0 Mode.

FIGURE 5-5: Serial Bus Sequence for Daisy-Chain Configuration; SPI™ 1,1 Mode.

## 6.0 APPLICATIONS INFORMATION

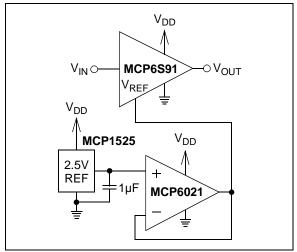

# 6.1 Changing External Reference Voltage

Figure 6-1 shows a MCP6S91 with the  $V_{REF}$  pin at 2.5V and  $V_{DD}$  = 5.0V. This allows the PGA to amplify signals centered on 2.5V, instead of ground-referenced signals. The voltage reference MCP1525 is buffered by a MCP6021, which gives a low output impedance reference voltage from DC to high frequencies. The source driving the  $V_{REF}$  pin should have an output impedance less than  $0.1\Omega$  to maintain reasonable gain accuracy.

**FIGURE 6-1:** PGA with Different External Reference Voltage.

## 6.2 Capacitive Load and Stability

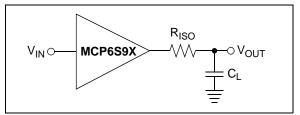

Large capacitive loads can cause stability problems and reduced bandwidth for the MCP6S91/2/3 family of PGAs (Figure 2-26 and Figure 2-28). As the load capacitance increases, there is a corresponding increase in frequency response peaking and step response overshoot and ringing. This happens because a large load capacitance decreases the internal amplifier's phase margin and bandwidth.

When driving large capacitive loads with these PGAs (i.e., > 60 pF), a small series resistor at the output (R<sub>ISO</sub> in Figure 6-2) improves the internal amplifier's stability by making the load resistive at higher frequencies. The bandwidth will be generally lower than the bandwidth with no capacitive load.

**FIGURE 6-2:** PGA Circuit for Large Capacitive Loads.

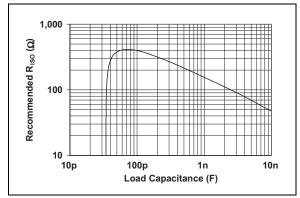

Figure 6-3 gives recommended  $R_{ISO}$  values for different capacitive loads. After selecting  $R_{ISO}$  for your circuit, double-check the resulting frequency response peaking and step response overshoot on the bench. Modify  $R_{ISO}$ 's value until the response is reasonable at all gains.

**FIGURE 6-3:** Recommended  $R_{ISO}$ .

## 6.3 Layout Considerations

Good PC board layout techniques will help achieve the performance shown in the Electrical Characteristics and Typical Performance Curves. It will also help minimize Electromagnetic Compatibility (EMC) issues.

## 6.3.1 COMPONENT PLACEMENT

Separate different circuit functions: digital from analog, low-speed from high-speed, and low-power from high-power. This will reduce crosstalk.

Keep sensitive traces short and straight. Separate them from interfering components and traces. This is especially important for high-frequency (low rise time) signals.

#### 6.3.2 SUPPLY BYPASS

Use a local bypass capacitor (0.01  $\mu$ F to 0.1  $\mu$ F) within 2 mm of the V<sub>DD</sub> pin. It must connect directly to the ground plane. A multi-layer ceramic chip capacitor, or high-frequency equivalent, works best.

Use a bulk bypass capacitor (2.2  $\mu$ F to 10  $\mu$ F) within 100 mm of the V<sub>DD</sub> pin. It needs to connect to the ground plane. A multi-layer ceramic chip capacitor, tantalum or high-frequency equivalent, works best. This capacitor may be shared with other nearby analog parts.

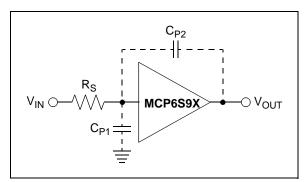

#### 6.3.3 INPUT SOURCE IMPEDANCE

The sources driving the inputs of the PGAs need to have reasonably low source impedance at higher frequencies. Figure 6-4 shows how the external source impedance ( $R_S$ ), PGA package pin capacitance ( $C_{P1}$ ) and PGA package pin-to-pin capacitance ( $C_{P2}$ ) form a positive feedback voltage divider network. Feedback to the selected channel may cause frequency response peaking and step response overshoot and ringing. Feedback to an unselected channel will produce crosstalk.

FIGURE 6-4: Positive Feedback Path.

Figure 2-6 shows the crosstalk (referred to input) that results when a hostile signal is connected to CH1, input CH0 is selected and  $R_{S}$  is connected from CH0 to GND. A gain of +32 was chosen for this plot because it demonstrates the worst-case behavior. Increasing  $R_{S}$  increases the crosstalk as expected. At a source impedance of 10  $k\Omega,$  there is noticeable peaking in the response; this is due to positive feedback.

Most designs should use a source resistance ( $R_S$ ) no larger than 10  $k\Omega$ . Careful attention to layout parasitics and proper component selection will help minimize this effect. When a source impedance larger than 10  $k\Omega$  must be used, place a capacitor in parallel to  $C_{P1}$  to reduce the positive feedback. This capacitor needs to be large enough to overcome gain (or crosstalk) peaking, yet small enough to allow a reasonable signal bandwidth.

#### 6.3.4 SIGNAL COUPLING

The input pins of the MCP6S91/2/3 family of PGAs are high-impedance. This makes them especially susceptible to capacitively-coupled noise. Using a ground plane helps reduce this problem.

When noise is capacitively coupled, the ground plane provides additional shunt capacitance to ground. When noise is magnetically coupled, the ground plane reduces the mutual inductance between traces. Increasing the separation between traces makes a significant difference.

Changing the direction of one of the traces can also reduce magnetic coupling. It may help to locate guard traces next to the victim trace. They should be on both sides of, and as close as possible to, the victim trace. Connect the guard traces to the ground plane at both ends. Also connect long guard traces to the ground plane in the middle.

#### 6.3.5 HIGH-FREQUENCY ISSUES

Because the MCP6S91/2/3 PGAs' frequency response reaches unity gain at 64 MHz when G=16 and 32, it is important to use good PCB layout techniques. Any parasitic-coupling at high-frequency might cause undesired peaking. Filtering high-frequency signals (i.e., fast edge rates) can help. To minimize high-frequency problems:

- Use complete ground and power planes

- · Use HF, surface-mount components

- Provide clean supply voltages and bypassing

- · Keep traces short and straight

- Try a linear power supply (e.g., a LDO)

## 6.4 Typical Applications

#### 6.4.1 GAIN RANGING

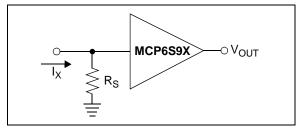

Figure 6-5 shows a circuit that measures the current  $I_X$ . The circuit's performance benefits from changing the gain on the PGA. Just as a hand-held multimeter uses different measurement ranges to obtain the best results, this circuit makes it easy to set a high gain for small signals and a low gain for large signals. As a result, the required dynamic range at the PGA's output is less than at its input (by up to 30 dB).

**FIGURE 6-5:** Wide Dynamic Range Current Measurement Circuit.

#### 6.4.2 SHIFTED GAIN RANGE PGA

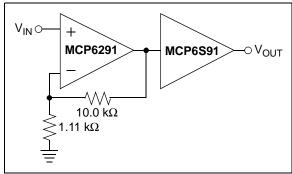

Figure 6-6 shows a circuit using a MCP6291 at a gain of +10 in front of a MCP6S91. This shifts the overall gain range to +10 V/V to +320 V/V (from +1 V/V to +32 V/V).

**FIGURE 6-6:** PGA with Higher Gain Range.

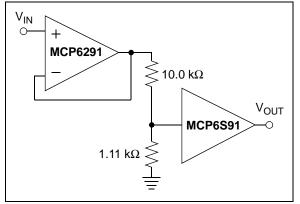

It is also easy to shift the gain range to lower gains (see Figure 6-7). The MCP6291 acts as a unity gain buffer, and the resistive voltage divider shifts the gain range down to +0.1 V/V to +3.2 V/V (from +1 V/V to +32 V/V).

**FIGURE 6-7:** PGA with Lower Gain Range.

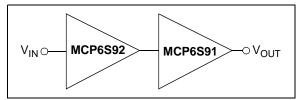

#### 6.4.3 EXTENDED GAIN RANGE PGA

Figure 6-8 gives a +1 V/V to +1024 V/V gain range, which is much greater than the range for a single PGA (+1 V/V to +32 V/V). The first PGA provides input multiplexing capability, while the second PGA only needs one input. These devices can be daisy-chained (Section 5.3 "Daisy-Chain Configuration").

**FIGURE 6-8:** PGA with Extended Gain Range.

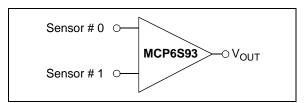

#### 6.4.4 MULTIPLE SENSOR AMPLIFIER

The multiple-channel PGAs (MCP6S92 and MCP6S93) allow the user to select which sensor appears on the output (see Figure 6-9). These devices can also change the gain to optimize performance for each sensor.

**FIGURE 6-9:** PGA with Multiple Sensor Inputs.

#### 6.4.5 EXPANDED INPUT PGA

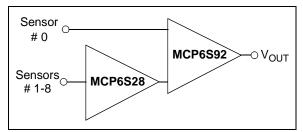

Figure 6-10 shows cascaded MCP6S28 and MCP6S92s PGAs that provide up to 9 input channels. Obviously, Sensors #1-8 have a high total gain range available, as explained in **Section 6.4.3 "Extended Gain Range PGA"**. These devices can be daisy-chained (**Section 5.3 "Daisy-Chain Configuration"**).

FIGURE 6-10: PGA with Expanded Inputs.

## 6.4.6 PICmicro® MCU WITH EXPANDED INPUT CAPABILITY

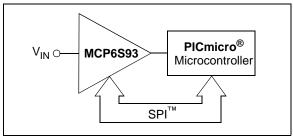

Figure 6-11 shows a MCP6S93 driving an analog input to a PICmicro microcontroller. This greatly expands the input capacity of the microcontroller, while adding the ability to select the appropriate gain for each source.

**FIGURE 6-11:** Expanded Input for a PICmicro<sup>®</sup> Microcontroller.

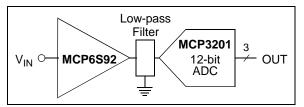

#### 6.4.7 ADC DRIVER

This family of PGAs is well suited for driving Analog-to-Digital Converters (ADCs). The binary gains (1, 2, 4, 8, 16 and 32) effectively add five more bits to the input range (see Figure 6-12). This works well for applications needing relative accuracy more than absolute accuracy (e.g., power monitoring).

FIGURE 6-12: PGA as an ADC driver.

At low gains, the ADC's Signal-to-Noise Ratio (SNR) will dominate since the PGA's input noise voltage density is so low (10 nV/ $\sqrt{\text{Hz}}$  @ 10 kHz, typ.). At high gains, the PGA's noise will dominate the SNR, but it is low enough to support most applications. These PGAs add the flexibility of selecting the best gain for an application.

The low-pass filter in the block diagram reduces the integrated noise at the MCP6S92's output and serves as an anti-aliasing filter. This filter may be designed using Microchip's FilterLab<sup>®</sup> software, available at www.microchip.com.

## 7.0 PACKAGING INFORMATION

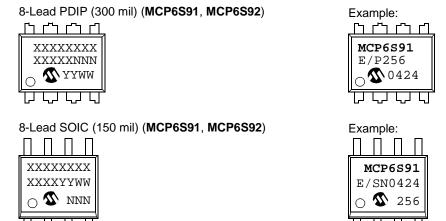

## 7.1 Package Marking Information

Example:

| Legend | XXX<br>YY<br>WW<br>NNN | Customer specific information* Year code (last 2 digits of calendar year) Week code (week of January 1 is week '01') Alphanumeric traceability code                       |

|--------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried             | nt the full Microchip part number cannot be marked on one line, it will lover to the next line thus limiting the number of available characters her specific information. |

<sup>\*</sup> Standard marking consists of Microchip part number, year code, week code, traceability code (facility code, mask rev#, and assembly code). For marking beyond this, certain price adders apply. Please check with your Microchip Sales Office.

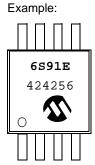

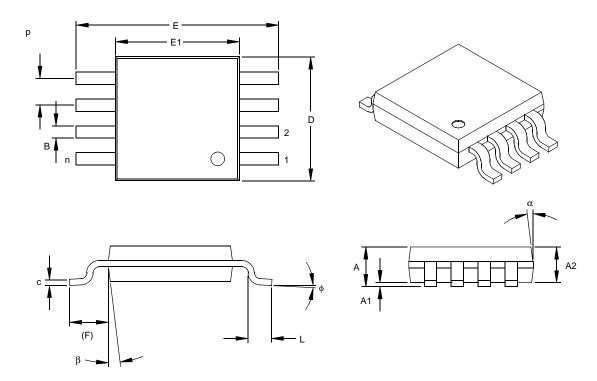

## 8-Lead Plastic Dual In-line (P) - 300 mil (PDIP)

|                            | Units      | Units INCHES* |      |      | MILLIMETERS |      |       |  |

|----------------------------|------------|---------------|------|------|-------------|------|-------|--|

| Dimensi                    | ion Limits | s MIN NOM I   |      | MAX  | MIN         | NOM  | MAX   |  |

| Number of Pins             | n          |               | 8    |      |             | 8    |       |  |

| Pitch                      | р          |               | .100 |      |             | 2.54 |       |  |

| Top to Seating Plane       | Α          | .140          | .155 | .170 | 3.56        | 3.94 | 4.32  |  |

| Molded Package Thickness   | A2         | .115          | .130 | .145 | 2.92        | 3.30 | 3.68  |  |

| Base to Seating Plane      | A1         | .015          |      |      | 0.38        |      |       |  |

| Shoulder to Shoulder Width | Е          | .300          | .313 | .325 | 7.62        | 7.94 | 8.26  |  |

| Molded Package Width       | E1         | .240          | .250 | .260 | 6.10        | 6.35 | 6.60  |  |

| Overall Length             | D          | .360          | .373 | .385 | 9.14        | 9.46 | 9.78  |  |

| Tip to Seating Plane       | L          | .125          | .130 | .135 | 3.18        | 3.30 | 3.43  |  |

| Lead Thickness             | С          | .008          | .012 | .015 | 0.20        | 0.29 | 0.38  |  |

| Upper Lead Width           | B1         | .045          | .058 | .070 | 1.14        | 1.46 | 1.78  |  |

| Lower Lead Width           | В          | .014          | .018 | .022 | 0.36        | 0.46 | 0.56  |  |

| Overall Row Spacing        | § eB       | .310          | .370 | .430 | 7.87        | 9.40 | 10.92 |  |

| Mold Draft Angle Top       | α          | 5             | 10   | 15   | 5           | 10   | 15    |  |

| Mold Draft Angle Bottom    | β          | 5             | 10   | 15   | 5           | 10   | 15    |  |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-001

Drawing No. C04-018

<sup>\*</sup> Controlling Parameter § Significant Characteristic

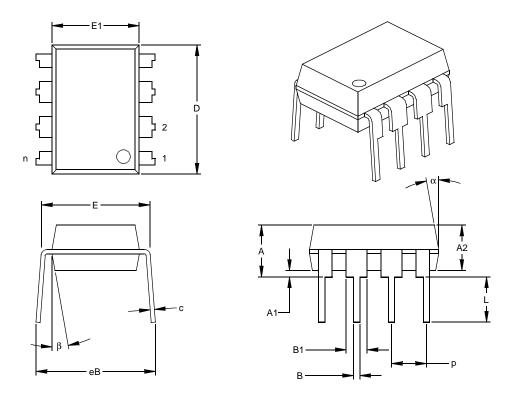

## 8-Lead Plastic Small Outline (SN) - Narrow, 150 mil (SOIC)

|                          | Units  |      | INCHES* |      | N    | 3    |      |

|--------------------------|--------|------|---------|------|------|------|------|

| Dimension                | Limits | MIN  | NOM     | MAX  | MIN  | NOM  | MAX  |

| Number of Pins           | n      |      | 8       |      |      | 8    |      |

| Pitch                    | р      |      | .050    |      |      | 1.27 |      |

| Overall Height           | Α      | .053 | .061    | .069 | 1.35 | 1.55 | 1.75 |

| Molded Package Thickness | A2     | .052 | .056    | .061 | 1.32 | 1.42 | 1.55 |

| Standoff §               | A1     | .004 | .007    | .010 | 0.10 | 0.18 | 0.25 |

| Overall Width            | Е      | .228 | .237    | .244 | 5.79 | 6.02 | 6.20 |

| Molded Package Width     | E1     | .146 | .154    | .157 | 3.71 | 3.91 | 3.99 |

| Overall Length           | D      | .189 | .193    | .197 | 4.80 | 4.90 | 5.00 |

| Chamfer Distance         | h      | .010 | .015    | .020 | 0.25 | 0.38 | 0.51 |

| Foot Length              | L      | .019 | .025    | .030 | 0.48 | 0.62 | 0.76 |

| Foot Angle               | ф      | 0    | 4       | 8    | 0    | 4    | 8    |

| Lead Thickness           | С      | .008 | .009    | .010 | 0.20 | 0.23 | 0.25 |

| Lead Width               | В      | .013 | .017    | .020 | 0.33 | 0.42 | 0.51 |

| Mold Draft Angle Top     | α      | 0    | 12      | 15   | 0    | 12   | 15   |

| Mold Draft Angle Bottom  | β      | 0    | 12      | 15   | 0    | 12   | 15   |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-012

Drawing No. C04-057

<sup>\*</sup> Controlling Parameter § Significant Characteristic

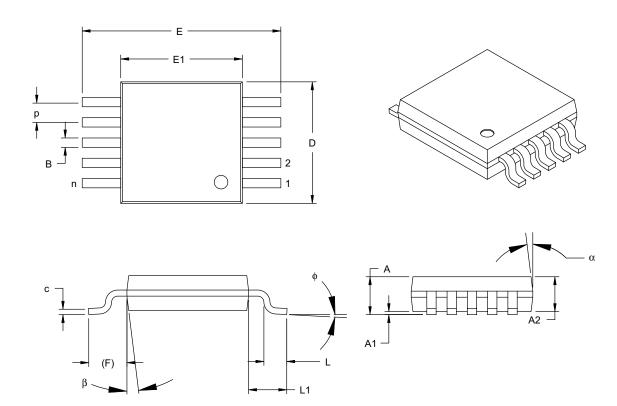

## 8-Lead Plastic Micro Small Outline Package (MS) (MSOP)

|                          | Units |      | INCHES |      |      | MILLIMETERS* |       |  |

|--------------------------|-------|------|--------|------|------|--------------|-------|--|

| Dimension I              | imits | MIN  | NOM    | MAX  | MIN  | NOM          | MAX   |  |

| Number of Pins           | n     |      | 8      |      |      |              | 8     |  |

| Pitch                    | р     |      | .026   |      |      | 0.65         |       |  |

| Overall Height           | Α     |      |        | .044 |      |              | 1.18  |  |

| Molded Package Thickness | A2    | .030 | .034   | .038 | 0.76 | 0.86         | 0.97  |  |

| Standoff §               | A1    | .002 |        | .006 | 0.05 |              | 0.15  |  |

| Overall Width            | E     | .184 | .193   | .200 | 4.67 | 4.90         | .5.08 |  |

| Molded Package Width     | E1    | .114 | .118   | .122 | 2.90 | 3.00         | 3.10  |  |

| Overall Length           | D     | .114 | .118   | .122 | 2.90 | 3.00         | 3.10  |  |

| Foot Length              | L     | .016 | .022   | .028 | 0.40 | 0.55         | 0.70  |  |

| Footprint (Reference)    | F     | .035 | .037   | .039 | 0.90 | 0.95         | 1.00  |  |

| Foot Angle               | ф     | 0    |        | 6    | 0    |              | 6     |  |

| Lead Thickness           | С     | .004 | .006   | .008 | 0.10 | 0.15         | 0.20  |  |

| Lead Width               | В     | .010 | .012   | .016 | 0.25 | 0.30         | 0.40  |  |

| Mold Draft Angle Top     | α     |      | 7      |      |      | 7            |       |  |

| Mold Draft Angle Bottom  | β     |      | 7      |      |      | 7            |       |  |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

Drawing No. C04-111

<sup>\*</sup>Controlling Parameter § Significant Characteristic

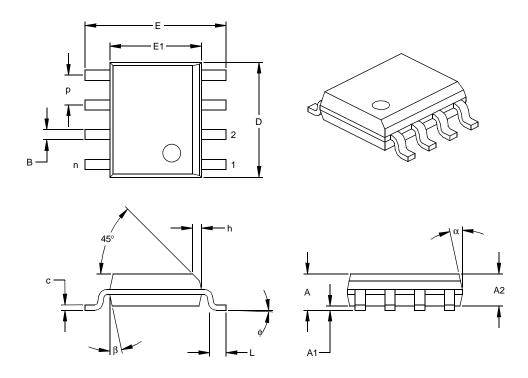

## 10-Lead Plastic Micro Small Outline Package (MS) (MSOP)

|                          | Units            |      | INCHES   |      |          | MILLIMETERS* |      |  |

|--------------------------|------------------|------|----------|------|----------|--------------|------|--|

| Dimension L              | Dimension Limits |      | NOM      | MAX  | MIN      | NOM          | MAX  |  |

| Number of Pins           | n                |      | 10       |      |          | 10           |      |  |

| Pitch                    | р                |      | .020 TYP |      |          | 0.50 TYP.    |      |  |

| Overall Height           | Α                | -    | -        | .043 | -        | -            | 1.10 |  |

| Molded Package Thickness | A2               | .030 | .033     | .037 | 0.75     | 0.85         | 0.95 |  |

| Standoff                 | A1               | .000 | -        | .006 | 0.00     | -            | 0.15 |  |

| Overall Width            | E                |      | .193 BSC |      | 4.90 BSC |              |      |  |

| Molded Package Width     | E1               |      | .118 BSC |      | 3.00 BSC |              |      |  |

| Overall Length           | D                |      | .118 BSC |      | 3.00 BSC |              |      |  |

| Foot Length              | L                | .016 | .024     | .031 | 0.40     | 0.60         | 0.80 |  |

| Footprint                | F                |      | .037 REF |      |          | 0.95 REF     |      |  |

| Foot Angle               | ф                | 0°   | -        | 8°   | 0°       | -            | 8°   |  |

| Lead Thickness           | С                | .003 | -        | .009 | 0.08     | -            | 0.23 |  |

| Lead Width               | В                | .006 | .009     | .012 | 0.15     | 0.23         | 0.30 |  |

| Mold Draft Angle Top     | α                | 5°   | -        | 15°  | 5°       | -            | 15°  |  |

| Mold Draft Angle Bottom  | β                | 5°   | -        | 15°  | 5°       | -            | 15°  |  |

<sup>\*</sup>Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MO-187

Drawing No. C04-021

| M   | CF  | <b>26</b> S | 91 | 12 | 13 |

|-----|-----|-------------|----|----|----|

| IVI | VI. | UU          | JI |    | J  |

| N | 0 | т | F | S |  |

|---|---|---|---|---|--|

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.           | <u>-x</u> /xx                                                                                                                                                                    | Exa | amples:        |                                                        |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|--------------------------------------------------------|

| Device Temp        | <br>perature Package                                                                                                                                                             | a)  | MCP6S91-E/P:   | One-channel PGA,<br>PDIP package.                      |

| Ra                 | inge                                                                                                                                                                             | b)  | MCP6S91-E/SN:  | One-channel PGA,<br>SOIC package.                      |

| Device:            | MCP6S91: One-channel PGA                                                                                                                                                         | c)  | MCP6S91-E/MS:  | One-channel PGA,<br>MSOP package.                      |

|                    | MCP6S91T: One-channel PGA (Tape and Reel for SOIC and MSOP-8) MCP6S92: Two-channel PGA                                                                                           | a)  | MCP6S92-E/MS:  | Two-channel PGA,<br>MSOP-8 package.                    |

|                    | MCP6S92T: Two-channel PGA (Tape and Reel for SOIC and MSOP-8) MCP6S93: Two-channel PGA                                                                                           | b)  | MCP6S92T-E/MS: | Tape and Reel,<br>Two-channel PGA,<br>MSOP-8 package.  |

|                    | MCP6S93T: Two-channel PGA<br>(Tape and Reel for MSOP-10)                                                                                                                         | a)  | MCP6S93-E/UN:  | Two-channel PGA,<br>MSOP-10 package.                   |

| Temperature Range: | E = -40°C to +125°C                                                                                                                                                              | b)  | MCP6S93T-E/UN: | Tape and Reel,<br>Two-channel PGA,<br>MSOP-10 package. |

| Package:           | MS = Plastic Micro Small Outline (MSOP), 8-lead P = Plastic DIP (300 mil Body), 8-lead SN = Plastic SOIC (150 mil Body), 8-lead UN = Plastic Micro Small Outline (MSOP), 10-lead |     |                |                                                        |

## **Sales and Support**

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Corporate Literature Center U.S. FAX: (480) 792-7277

- 3. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

## MCP6S91/2/3

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."